Pinout ➡️ICI⬅️

Gestion de l'alimentation de l'ordinateur - port $600801 (BYTE)

Le bit 0 de ce registre pilote la broche 88 de l'ASIC. (sortie)

Pour éteindre électriquement le jouet, la valeur doit être basculé à $0.

L'état de cette broche ne semble pas influencer le comportement interne de la puce.

A l'allumage de l'ordinateur, sa valeur DOIT ETRE basculé à $1 (sinon, il s'éteindra au bout d'environ 700 millisecondes.)

Status du port cartouche - port $600803 (BYTE)

Le bit 0 et 1 de ce registre est piloté par la broche 48 et 152 de l'ASIC. (entrée)

Renvoie $3 si aucune cartouche est insérée.

Renvoie $2 si la cartouche d'activité n°2 est insérée (strap uniquement)

Renvoie $1 si la cartouche d'activité n°1 est insérée (strap uniquement)

Renvoie $0 si une cartouche avec une ROM/FLASH est insérée. (straps et ROM/FLASH)

Le port parallèle // - port $600101 (BYTE)

L'octet pilote la broche 57, 59, 61, 62, 63 65, 67 et 69 de l'ASIC. (sortie)

Port $600101.b (ecriture) - ecris l'octet sur le port parallèle.

Port $600101.b (lecture) - renvoie le status du port parallèle (ainsi que l'UART...)

L'octet en lecture 0bZ???Y??X

Donne : Z (128) représente l'état de BUSY, Y (8) représente l'état de ERROR et X (1) représente le status de l'UART.

Le clavier et la souris - port $600300 (WORD) + port $600301 (BYTE)

Ces registres sont internes, mais font le lien avec le chipset clavier/souris via la broche 103 et 104 de l'ASIC. (La broche 105 fournit l'horloge de 2 Mhz)

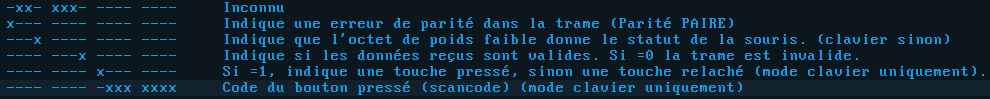

Port $600300.w (lecture seule) - Registre d'état de la dernière information reçu.

Ce registre est automatiquement gérée par la puce en arrière plan. Elle contient la trame d'informations concernant le clavier et la souris.

Aussi, la puce génère une interruption (IRQ TODO) dès que des données sont disponibles.

Format des données en mémoire:

Port $600301.b (BYTE) - Ecriture des registres internes du clavier.

Ce registre permet de configurer le controleur clavier/souris. Ce registre permet par exemple de changer les LED allumés (caps lock...).

NOTE: Il est nécessaire d'activer le bit3 du registre $600501 (TODO:pourquoi?) ; ori.b #8,($600501).l

Commande $F9 (Contrôle des LED) ; bit1 et bit2 définissent les leds :

0b0000 0CN0 (C= LED Caps lock/Ver. Maj. - N=Num lock/Verr num.)

En lecture (du registre $600301):

Le bit 3 informe sur le statut du message (envoyé/en cours d'envoi). (1=signifie correctement envoyé)

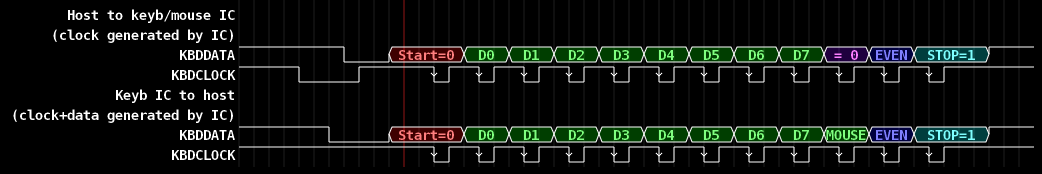

Ci-dessous, une trame représentant les données circulant dans les broches. Cela ressemble un peu à du PS2 sauf quelques modifications. :

Quand l'hôte envoie des donnés, seule la broche DATA est piloté par le chipset VTECH, sinon on pilote les 2 broches.

Quand l'hôte envoie des donnés, seule la broche DATA est piloté par le chipset VTECH, sinon on pilote les 2 broches.

A noter que le pilotage des broches se fait en open-collector.

▶️ L'UART :

La réception de données - port $600007 (BYTE) + $600001 (BYTE)

La broche 55 de l'ASIC est utilisée pour la réception des données

Port $600007.b (lecture) - L'octet reçu de l'UART

NOTE: Un drapeau est levé sur bit0 de $600001.b si une donnée valide à été reçu. Une interruption est aussi déclanché. TODO IRQ

La réception des données se fait systématiquement à la vitesse de 9600 baud, 1 bit de stop, aucun bit de parité.

L'emission de données - port $600101 (BYTE) + $600007 (BYTE)

L'UART à base de GAL16 et de 4060 utilise les broches du port // + 49, 60 et 71 de l'ASIC. (sortie/entrée)

Port $600101.b (écriture) - L'octet à envoyer par l'UART (le port est le même que le port parallèle, car les 2 sont multiplexés)

ATTENTION: L'octet ne sera pas envoyé tant que $600007.b (écriture) n'a pas réinitialisé à $00!

NOTE: Un drapeau est levé sur bit0 de $600101.b (lecture) quand la donnée à été bien envoyée. Pour passer l'UART en 9600 bauds entrée/sortie, il est nécessaire AVANT utilisation d'écrire la valeur $C1 au port $600003.b

Crédit photo de la breadboard : Ben Eater

Crédit photo du clavier : Mathieu Benoit

Crédit photo du DE-9 (hé oui, c'est pas DB-9!): Mike1024