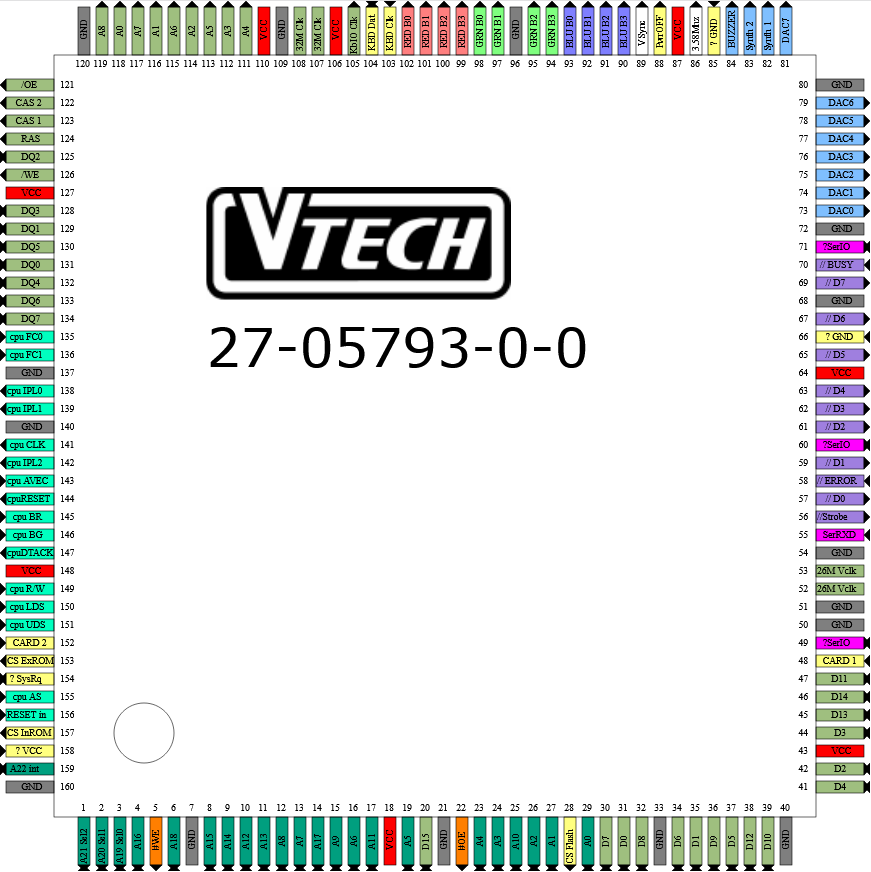

Pinout du chipset VTECH 27-05793-0-0 :

Tension d'alimentation : 5 volts (MAX : 5.5 v)

Courant utilisée (en moyenne): ~200 mA (MAX : 500 mA)

(Pas de signaux analogiques)

Pinout : VTECH 27-05793-0-0.ods

| Pin number | Sub-section | Pin name | I/O ? | Pin description |

|---|---|---|---|---|

| 1 | ADDRESS_BUS | A21 | Output | |

| 2 | ADDRESS_BUS | A20 | Output | |

| 3 | ADDRESS_BUS | A19 | Output | |

| 4 | ADDRESS_BUS | A16 | Output | |

| 5 | CONTROL_BUS | #WE | Output | |

| 6 | ADDRESS_BUS | A18 | Output | |

| 7 | POWER | GND | PWR | |

| 8 | ADDRESS_BUS | A15 | Output | |

| 9 | ADDRESS_BUS | A14 | Output | |

| 10 | ADDRESS_BUS | A12 | Output | |

| 11 | ADDRESS_BUS | A13 | Output | |

| 12 | ADDRESS_BUS | A8 | Output | |

| 13 | ADDRESS_BUS | A7 | Output | |

| 14 | ADDRESS_BUS | A17 | Output | |

| 15 | ADDRESS_BUS | A9 | Output | |

| 16 | ADDRESS_BUS | A6 | Output | |

| 17 | ADDRESS_BUS | A11 | Output | |

| 18 | POWER | VCC | PWR | |

| 19 | ADDRESS_BUS | A5 | Output | |

| 20 | DATA_BUS | D15 | IO + Z | |

| 21 | POWER | GND | PWR | |

| 22 | CONTROL_BUS | #OE | Output | |

| 23 | ADDRESS_BUS | A4 | Output | |

| 24 | ADDRESS_BUS | A3 | Output | |

| 25 | ADDRESS_BUS | A10 | Output | |

| 26 | ADDRESS_BUS | A2 | Output | |

| 27 | ADDRESS_BUS | A1 | Output | |

| 28 | CONTROL_BUS | #CS (Flash memory) | Output | When low, the flash memory (8 bit) is selected |

| 29 | ADDRESS_BUS | A0 | Output | |

| 30 | DATA_BUS | D7 | IO + Z | |

| 31 | DATA_BUS | D0 | IO + Z | |

| 32 | DATA_BUS | D8 | IO + Z | |

| 33 | POWER | GND | PWR | |

| 34 | DATA_BUS | D6 | IO + Z | |

| 35 | DATA_BUS | D15 | IO + Z | |

| 36 | DATA_BUS | D9 | IO + Z | |

| 37 | DATA_BUS | D5 | IO + Z | |

| 38 | DATA_BUS | D12 | IO + Z | |

| 39 | DATA_BUS | D10 | IO + Z | |

| 40 | POWER | GND | PWR | |

| 41 | DATA_BUS | D4 | IO + Z | |

| 42 | DATA_BUS | D2 | IO + Z | |

| 43 | POWER | VCC | PWR | |

| 44 | DATA_BUS | D3 | IO + Z | |

| 45 | DATA_BUS | D13 | IO + Z | |

| 46 | DATA_BUS | D14 | IO + Z | |

| 47 | DATA_BUS | D11 | IO + Z | |

| 48 | GENERAL_IO | SIG_CARD1 | Input | When low (a dumb cardridge type 1 has been inserted) |

| 49 | UART_IO | ?? SerIO ?? | ?? | |

| 50 | POWER | GND | PWR | |

| 51 | POWER | GND | PWR | |

| 52 | VIDEO | CLK_26MHZ | Output | |

| 53 | VIDEO | CLK_26MHZ | Input | Clock for the internal video subsection |

| 54 | POWER | GND | PWR | |

| 55 | UART_IO | UART RX | Input | |

| 56 | PARALLEL_PORT_IO | PP_STOBE | Output | |

| 57 | PARALLEL_PORT_IO | PP_D0 | Output | Pin shared with the UART TX daughter board |

| 58 | PARALLEL_PORT_IO | PP_ERROR | Input | |

| 59 | PARALLEL_PORT_IO | PP_D1 | Output | Pin shared with the UART TX daughter board |

| 60 | UART_IO | ?? SerIO ?? | ?? | |

| 61 | PARALLEL_PORT_IO | PP_D2 | Output | Pin shared with the UART TX daughter board |

| 62 | PARALLEL_PORT_IO | PP_D3 | Output | Pin shared with the UART TX daughter board |

| 63 | PARALLEL_PORT_IO | PP_D4 | Output | Pin shared with the UART TX daughter board |

| 64 | POWER | VCC | PWR | |

| 65 | PARALLEL_PORT_IO | PP_D5 | Output | Pin shared with the UART TX daughter board |

| 66 | POWER | GND ? | Input ? | |

| 67 | PARALLEL_PORT_IO | PP_D6 | Output | Pin shared with the UART TX daughter board |

| 68 | POWER | GND | PWR | |

| 69 | PARALLEL_PORT_IO | PP_D7 | Output | Pin shared with the UART TX daughter board |

| 70 | PARALLEL_PORT_IO | BUSY | Input | Pin shared with the UART TX daughter board |

| 71 | UART_IO | ?? SerIO ?? | ?? | |

| 72 | POWER | GND | PWR | |

| 73 | ADPCM_AUDIO | DAC0 | Output | |

| 74 | ADPCM_AUDIO | DAC1 | Output | |

| 75 | ADPCM_AUDIO | DAC2 | Output | |

| 76 | ADPCM_AUDIO | DAC3 | Output | |

| 77 | ADPCM_AUDIO | DAC4 | Output | |

| 78 | ADPCM_AUDIO | DAC5 | Output | |

| 79 | ADPCM_AUDIO | DAC6 | Output | |

| 80 | POWER | GND | PWR | |

| 81 | ADPCM_AUDIO | DAC7 | Output | |

| 82 | PWM_AUDIO | Synth1 | Output | Generate a 65Khz PWM Audio signal (channel 1) |

| 83 | PWM_AUDIO | Synth2 | Output | Generate a 65Khz PWM Audio signal (channel 2) |

| 84 | BUZZER_AUDIO | BUZZER | Output | |

| 85 | POWER | GND ? | Input ? | |

| 86 | VIDEO | 3.58 Mhz OUT | Output | |

| 87 | POWER | VCC | PWR | |

| 88 | GENERAL_IO | #PowerOFF | Output | (used by the power submodule, when low, a transistor cuts the VCC rail) |

| 89 | VIDEO | Vsync | Output | Video sync (~15 Khz) |

| 90 | VIDEO | BLUE_B3 | Output | |

| 91 | VIDEO | BLUE_B2 | Output | |

| 92 | VIDEO | BLUE_B1 | Output | |

| 93 | VIDEO | BLUE_B0 | Output | |

| 94 | VIDEO | GREEN_B3 | Output | |

| 95 | VIDEO | GREEN_B2 | Output | |

| 96 | POWER | GND | PWR | |

| 97 | VIDEO | GREEN_B1 | Output | |

| 98 | VIDEO | GREEN_B0 | Output | |

| 99 | VIDEO | RED_B3 | Output | |

| 100 | VIDEO | RED_B2 | Output | |

| 101 | VIDEO | RED_B1 | Output | |

| 102 | VIDEO | RED_B0 | Output | |

| 103 | GENERAL_IO | KBD_Clk | Input | Clock generated by the peripherical (like PS/2 keyboard) |

| 104 | GENERAL_IO | KBD_Data | IO | Must be pulled-up |

| 105 | GENERAL_IO | KBD_SysClock (2 Mhz) | Output | (=CLK_32MHZ / 16) |

| 106 | POWER | VCC | PWR | |

| 107 | GENERAL_IO | CLK_32MHZ | Output | |

| 108 | GENERAL_IO | CLK_32MHZ | Input | Main clock |

| 109 | POWER | GND | PWR | |

| 110 | POWER | VCC | PWR | |

| 111 | DRAM_IO | A4 | Output | |

| 112 | DRAM_IO | A3 | Output | |

| 113 | DRAM_IO | A5 | Output | |

| 114 | DRAM_IO | A2 | Output | |

| 115 | DRAM_IO | A6 | Output | |

| 116 | DRAM_IO | A1 | Output | |

| 117 | DRAM_IO | A7 | Output | |

| 118 | DRAM_IO | A0 | Output | |

| 119 | DRAM_IO | A8 | Output | |

| 120 | POWER | GND | PWR | |

| 121 | DRAM_IO | /OE | Output | |

| 122 | DRAM_IO | CAS2 | Output | |

| 123 | DRAM_IO | CAS1 | Output | |

| 124 | DRAM_IO | RAS | Output | |

| 125 | DRAM_IO | DQ2 | IO + Z | |

| 126 | DRAM_IO | /WE | Output | |

| 127 | POWER | VCC | PWR | |

| 128 | DRAM_IO | DQ3 | IO + Z | |

| 129 | DRAM_IO | DQ1 | IO + Z | |

| 130 | DRAM_IO | DQ5 | IO + Z | |

| 131 | DRAM_IO | DQ0 | IO + Z | |

| 132 | DRAM_IO | DQ4 | IO + Z | |

| 133 | DRAM_IO | DQ6 | IO + Z | |

| 134 | DRAM_IO | DQ7 | IO + Z | |

| 135 | CPU | CPU_FC0 | Input | |

| 136 | CPU | CPU_FC1 | Input | |

| 137 | POWER | GND | PWR | |

| 138 | CPU | CPU_IPL0 | Output | |

| 139 | CPU | CPU_IPL1 | Output | |

| 140 | POWER | GND | PWR | |

| 141 | CPU | CLK_CPU_16MHZ | Output | (=CLK_32MHZ / 2) |

| 142 | CPU | CPU_IPL2 | Output | |

| 143 | CPU | CPU_AVEC | Output | |

| 144 | CPU | CPU_RESET | Output | |

| 145 | CPU | CPU_BR | Output | Linked internally to the ADPCM FIFO (Empty) |

| 146 | CPU | CPU_BG | Input | Used by the ADPCM FIFO to take control of the bus |

| 147 | CPU | CPU_DTACK | Output | |

| 148 | POWER | VCC | PWR | |

| 149 | CPU | CPU_RW | Input | |

| 150 | CPU | CPU_LDS | Input | |

| 151 | CPU | CPU_UDS | Input | |

| 152 | GENERAL_IO | SIG_CARD2 | Input | When low (a dumb cardridge type 2 has been inserted) |

| 153 | CONTROL_BUS | #CS (Cardridge) | Output | When low, the cardridge port is selected |

| 154 | GENERAL_IO | ?? SYSRQ (Cardridge signal)?? | ?? | |

| 155 | CPU | CPU_AS | Input | |

| 156 | GENERAL_IO | RESET | Input | |

| 157 | CONTROL_BUS | #CS (Internal ROM) | Output | When low, the internal rom is selected |

| 158 | POWER | VCC ? | Input | |

| 159 | ADDRESS_BUS | A22 | Output | |

| 160 | POWER | GND | PWR |